# Ultrahigh-Performance Inverters Based on CdS Nanobelts

Peicai Wu, Yu Ye, Tuo Sun, Ruoming Peng, Xiaonan Wen, Wanjin Xu, Cui Liu, and Lun Dai\*

State Key Lab for Mesoscopic Physics and Department of Physics, Peking University, Beijing 100871, China

#### **ABSTRACT** We report ultrahigh-performance inverters, each consisting of two top-gate

metal—oxide—semiconductor field-effect transistors based on *n*-CdS nanobelts. High-IC HfO<sub>2</sub> dielectrics are used as the top-gate oxide layers. The inverters have a large supply voltage ( $V_{DD}$ ) range (from 50 mV to 10 V) and very high voltage gain ( $\sim$ 10, 100, and 1000 at  $V_{DD} = 0.2$ , 1, and 10 V, respectively). Current consumption is less than 7 nA at  $V_{DD} = 1$  V, corresponding to a power consumption of less than 7 nW. The high and low output voltages are close to full rail. The inverters also exhibit good dynamic behavior with square wave input at frequencies up to 1 kHz. The operation of the inverters is analyzed in detail. The inverters are promising for future low power high performance logic circuit applications.

KEYWORDS: CdS · high-κ dielectrics · nanobelt · field-effect transistors · inverter

\*Address correspondence to lundai@pku.edu.cn.

Received for review July 22, 2009 and accepted September 3, 2009.

Published online September 16, 2009. 10.1021/nn9008438 CCC: \$40.75

© 2009 American Chemical Society

emiconductor nanomaterials have shown their unique virtues as the building material for powerful electronic devices. Inverters are important building blocks in the integrated circuits. They can be constructed with field-effect transistors (FETs) of various materials. In the area of nanoelectronics, various types of inverters, such as resistor-load,<sup>1,2</sup> p -channel metal-oxide-semiconductor (PMOS),<sup>3-6</sup> n-channel MOS (NMOS), 7,8 complementary MOS (CMOS), <sup>9–15</sup> n-channel metal-semiconductor (NMES),<sup>16</sup> and complementary MES (CMES)<sup>17</sup> inverters have been developed based on various nanomaterials, such as thin films, nano-

wires/nanobelts (NWs/ NBs), carbon nanotubes (CNTs), and graphene. So far, most reported inverters based on semiconductor nanomaterials work under supply voltages (V<sub>DD</sub>) larger than 0.4 V and have voltage gain less than 100. Power consumption is an increasingly

important issue in general purpose processors. As transistors become smaller and faster, static power dissipation will increase significantly. Complementary inverters having both *n*- and *p*-channel transistors have a key inherent characteristic of low static power consumption. However, many important semiconductor nanoelectronic materials, such as CdS, CdSe, and Zn<sub>3</sub>P<sub>2</sub> etc., are unipolar materials.<sup>16–20</sup> In other words, they tend to exhibit only one conductivity type due to the strong self-compensation effect. This will limit their application in constructing high-performance complementary inverters. Exploring NMOS and/or PMOS inverters with improved performance characteristics, such as voltage gain, supply voltage, and power consumption, is still urgent in the practical application of nanomaterial circuits.

In this paper, we report NMOS inverters constructed with two top-gate MOS-FETs based on *n*-CdS NBs. The two MOS-FETs have different threshold voltages ( $V_{\rm th}$ ). The inverters can work under supply voltages down to 50 mV at room temperature and have a voltage gain of up to ~1000 at the  $V_{\rm DD}$  of 10 V. These characteristics, as far as we know, are the best

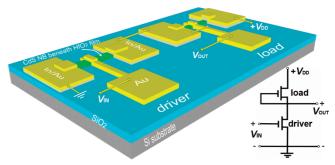

Figure 1. Schematic illustration of an as-fabricated inverter. The golden lines show the way the circuit is connected. The inset is the corresponding circuit diagram.

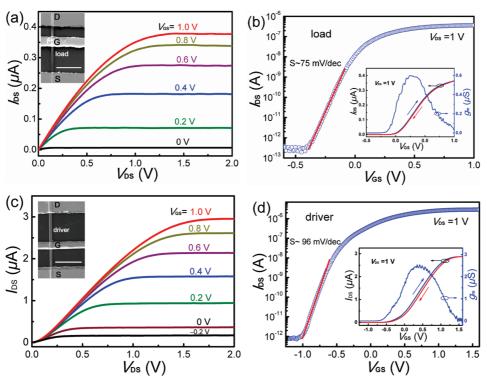

Figure 2. (a) A family of  $I_{DS}$  versus  $V_{DS}$  curves measured at different  $V_{GS}$  of the load MOSFET. The inset shows the FESEM image of the device (scale bar: 10  $\mu$ m). (b) Gate transfer characteristic of the load at  $V_{DS} = 1$  V. The straight red line highlights the subthreshold region. The inset shows the  $I_{DS} - V_{GS}$  hysteresis and transconductance curves. The curves in same color are measured simultaneously. (c) A family of  $I_{DS}$  versus  $V_{DS}$  curves measured at different  $V_{GS}$  of the driver MOSFET. The inset shows the FESEM image of the device (scale bar: 10  $\mu$ m). (d) Gate transfer characteristic of the driver at  $V_{DS} = 1$  V.

among the inverters based on nanomaterials reported so far. The current  $(I_{DD})$  flowing through the inverter  $(V_{DD} = 1 \text{ V})$  is less than 7 nA, corresponding to a power consumption of less than 7 nW, which is so far the lowest reported value for NMOS and/or PMOS inverters. The operation of the inverters is analyzed in detail. The dynamic characteristics of the inverters are also studied. The inverters show good dynamic behaviors with output rising and falling times of about 0.25 and 0.03 ms, respectively, at square wave input frequency up to 1 kHz.

## **RESULTS AND DISCUSSION**

Figure 1 shows the schematic illustration of an asfabricated inverter. The golden lines show the way the circuit is connected. The inset is the corresponding circuit diagram. Static electrical trans-port measurements were done with a semiconductor characterization system (Keithley 4200). Dynamic behaviors of the inverters were investigated with a digital oscilloscope (Tektronix DPO 2024) and square waves. All the measurements were done in darkness at room-temperature.

Figure 2a shows a family of source-drain current  $(I_{DS})$  versus source-drain voltage  $(V_{DS})$  curves measured at different gate voltages  $(V_{GS})$  of the load MOSFET. The inset is a field-emission scanning electron microscope (FESEM) image of this transistor. The NB used (NB A) is about 0.86  $\mu$ m wide and 133 nm thick. Figure 2b is the

gate transfer characteristics at  $V_{\rm DS} = 1$  V. An on/off ratio of about 6  $\times$  10<sup>6</sup> is obtained. The threshold voltage  $V_{\rm th}$  is very low (-0.1 V), which is beneficial to the low power inverter described below. The  $I_{DS} - V_{GS}$  relation in the subthreshold region (the straight red line) gives a subthreshold swing S of  $\sim$ 75 mV/dec. The inset shows the  $I_{DS} - V_{GS}$  hysteresis and transconductance  $(g_m)$ curves, which exhibit a very small hysteresis and a peak  $g_{\rm m}$  value of about 0.6  $\mu$ S, respectively. The field-effect electron mobility ( $\mu_e$ ) of this MOSFET can be estimated to be about 18.6 cm<sup>2</sup>/V · s using the equation  $\mu_e = L_C g_m/$  $(WC_0V_{DS})$ ,<sup>21</sup> where  $L_C$  is the channel length (20  $\mu$ m),  $C_0$ is the oxide capacitance per unit area (=  $\varepsilon_r \varepsilon_0/d$ ),  $\varepsilon_r$  is the relative dielectrics constant of HfO<sub>2</sub> ( $\sim$ 17), W is the gate width (equal to the width of NB in the FET) and d is the thickness (20 nm) of the HfO<sub>2</sub> layer. Decrease of mobility is commonly observed in MOSFETs with high-k dielectrics, which is attributed to the carrier scattering caused by interface states between the high-k dielectrics and the semiconductor conductive channel.<sup>18,21,22</sup> Figures 2c and 2d show the transfer characteristics of the driver MOSFET. The NB used (NB B) is about 1.1  $\mu$ m wide and 125 nm thick. This MOSFET has a V<sub>th</sub> of about -0.65 V, an on/off ratio of about 2  $\times$  10<sup>6</sup>, a subthreshold swing of about 96 mV/dec, and a peak  $q_{\rm m}$  value of about 2.5  $\mu$ S. The field-effect electron mobility of this MOSFET can be estimated to be about 60.5  $\text{cm}^2/\text{V} \cdot \text{s}$ using the above-mentioned equation. Figure 3a is the static voltage transfer characteristic (VTC) curves of the

VOL. 3 • NO. 10 • 3138-3142 • 2009

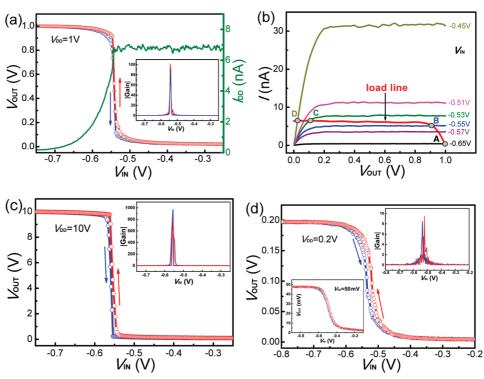

Figure 3. (a) Static VTC curves of the NMOS inverter under the  $V_{DD}$  of 1 V with  $V_{IN}$  being cycled. The arrows indicate the  $V_{IN}$  sweeping directions. The green curve shows the current flowing through the inverter ( $I_{DD}$ ) during the measurement (corresponding to the red VTC curve). The inset is the voltage gain curves obtained from the corresponding VTC curves. (b) Graphical determination of the static VTC of the inverter. A, B, C, and D are corresponding operating points at four representative  $V_{IN}$ . (c) VTC curves of the inverter under  $V_{DD}$  of 10 V. The inset is the corresponding voltage gain curves. (d) VTC curves of the inverter under  $V_{DD}$  of 0.2 V. The upper-right inset shows the corresponding voltage gain curves. The lower-left inset shows the VTC curves under an ultra low  $V_{DD}$  of 50 mV.

inverter constructed with the above-mentioned two transistors with the input voltage ( $V_{IN}$ ) being cycled  $(V_{DD} = 1 \text{ V})$ . The arrows indicate the  $V_{IN}$  sweeping directions. The high and low output voltages ( $V_{OH}$  and  $V_{OL}$ ) are close to the supply voltage  $V_{DD}$  and zero, respectively. The green curve shows the current flowing through the inverter (IDD) during the measurement (corresponding to the red VTC curve). It is clear that the  $I_{DD}$ is less than 7 nA during the whole measurement process, corresponding to a power consumption <7 nW, which is so far the lowest reported value for NMOS and/or PMOS inverters. The inset shows the voltage gain (=  $-dV_{OUT}/dV_{IN}$ ) curves obtained from the corresponding VTC curves. The peak gain value is as high as  $\sim$ 100, which is the best reported value, as far as we know, for inverters based on nanomaterials working at a supply voltage of 1 V.

To explain why the NMOS inverter exhibits such high performance, we have studied the operation of the inverters in detail. Figure 3b illustrates the graphical determination of the static VTC of the inverter (all the curves are the experimental results,  $V_{DD} = 1$  V). In our inverter, the gate and source of the load transistor are connected, hence the gate voltage of the load can always be taken as 0 V (*i.e.*,  $V_{GS-L} = 0$  V). Therefore, the  $I_{DS-L}-V_{DS-L}$  relation (*i.e.*,  $I_{DS}-V_{DS}$  relations of load transistor) at  $V_{GS-L} = 0$  V is the load line of the inverter. The marked A, B, C, and D are four representative intersec-

tions of the load line and the  $I_{DS-D} - V_{DS-D}$  curves ( $I_{DS} - V_{DS}$ relations of driver transistor) at various  $V_{IN}$  (=  $V_{GS-D}$ ), which reflect the actual operating points of the inverter. Since the load has a near-0  $V_{\rm th}$ , its saturation current at  $V_{GS-L} = 0$  V is very small (see Figure 2a,b), which directly results in low power consumption of this inverter. At operating point A,  $V_{IN}$  is -0.65 V (input logic 0), and the driver is cut off, resulting in a very small  $I_{DD}$  (see Figure 2c,d). Therefore,  $V_{OUT}$  is very close to  $V_{DD}$  ( $V_{OUT}$  =  $V_{DD} - V_{DS-L}$ ) (output logic 1). With  $V_{IN}$  increasing,  $V_{OUT}$  decreases. When  $V_{IN}$  changes from -0.55 to -0.53 V (corresponding to points B and C), VOUT decreases sharply from 0.9 to 0.1 V, corresponding to an ultrahigh voltage gain. When  $V_{IN}$  increases further to -0.45 V, the operating point reaches point D (input logic 1), and  $V_{OUT}$ is very close to zero (output logic 0). From this figure we can see that in our case, the perfect  $I_{DS} - V_{DS}$  saturation characteristics of both the load and driver transistors account for the ultrahigh voltage gain of the inverter, while the small saturation current for the load at  $V_{GS-L}$ = 0 V (corresponding to a near-0 V<sub>th</sub> for the load) accounts for the low power consumption and the nearideal  $V_{OH}$  and  $V_{OL}$  values.

Figure 3c shows the VTC curves of the inverter at  $V_{\text{DD}} = 10$  V. Maximum voltage gain can be as high as  $\sim 1000$  (see the inset) with very stable output voltage. Figure 3d shows the VTC curves of the inverter under  $V_{\text{DD}} = 0.2$  V. The peak gain is about 10 (see the upper-

SNANO

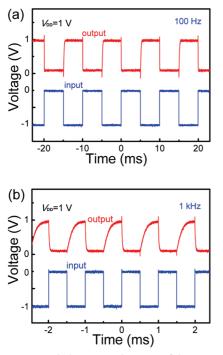

Figure 4. Dynamic behaviors (red curves) of the NMOS inverter driven by square wave with frequencies of 100 Hz (a) and 1 kHz (b) at V<sub>DD</sub> of 1 V. The blue curves show the corresponding square wave inputs.

right inset). The lower-left inset shows the VTC curves of the inverter under  $V_{DD} = 50$  mV. It can be clearly seen that the inverter still exhibits good inverting behavior under this ultra low supply voltage. As far as we know, this is the lowest reported supply voltage under which an inverter based on nanomaterials can still work with good inverting behaviors at room temperature. This low voltage behavior is valuable for low power consumption application.

We have also measured the dynamic behavior of the inverter driven by square wave with different frequencies at V<sub>DD</sub> of 1 V. The high and low levels of the input square wave are 0 and -1 V, respectively. At a

## The n-CdS NBs used for fabricating devices were synthe-

**EXPERIMENTS**

sized via an atmospheric vapor-liquid-solid (VLS) method.<sup>18</sup> During the synthesis process, CdS powders (99.995%) were placed at the upstream of Ar gas as the source. Si wafers covered with 10 nm thick thermally evaporated Au films were used as substrates. A tiny Cd grain (99.95%) was placed between the source and the substrates as the dopant. The temperatures at the source and substrate locations were about 850 and 750 °C, respectively. The dopant temperature could be changed from 750 to 850 °C by changing the position of Cd grain. By controlling the mass ratio of CdS to Cd and the position of Cd grain, we could partially control the electron concentration of the CdS NBs. The as-synthesized CdS NBs exhibited good n-type conductivity due to sulfur vacancies and/or cadmium interstitials, which serve as shallow donors.

The MOSFETs employed in the inverters were fabricated as follows: First, CdS NB suspension was dropped on oxidized Si substrates, each covered with a 400 nm thick SiO<sub>2</sub>

lower frequency of 100 Hz (Figure 4a), good inverting behaviors are clearly observed. At a higher frequency of 1 kHz (Figure 4b), RC delays at on and off switching are observed. The rising  $(t_r)$  and falling times  $(t_f)$  can be obtained to be about 0.25 and 0.03 ms, respectively, measured at 10% and 90% output values from Figure 4b. The delays mainly result from the overlap capacitance between the  $V_{IN}$  and  $V_{OUT}$  electrodes in our inverter structure.<sup>23–26</sup> The difference of  $t_r$  and  $t_f$  ( $t_r/t_f \cong$ 8) could be understood by considering the difference between the on-state current levels of load ( $\sim$ 0.35  $\mu$ A) and driver transistors ( $\sim$ 2.7  $\mu$ A) (see Figure 2b,d). Channel electrons charge and discharge the overlap capacitance region with the channel current of the driver being about 8 times larger than that of the load, resulting in  $t_r$  being about 8 times larger than  $t_f$ . The inverter can be further improved in the future to minimize the delays by using active semiconductor materials of higher carrier mobility and thinner gate dielectrics, shortening the channel length, and optimizing the measurement system.<sup>6</sup> Finally, it is worth noting that the performance of the inverters remain stable after they have been exposed to air continuously for 3 or more months.

## CONCLUSION

In summary, we have fabricated ultrahighperformance inverters, each consisting of two top-gate Au/HfO<sub>2</sub>/CdS NB MOSFETs. The inverters show many characteristics, such as large  $V_{DD}$  range (from 50 mV to 10 V), ultrahigh voltage gain, and low power consumption. The  $V_{OH}$  and  $V_{OL}$  are very close to full rail. The inverters also show good dynamic behavior with square wave input frequencies of up to 1 kHz. The performance of the inverters is stable with time. The operation of the inverters is analyzed in detail. These inverters are promising for future low power high performance logic circuit applications.

film. Second, UV lithography followed by thermal evaporation and lift-off process was used to fabricate ohmic contact In/Au electrodes (20/100 nm) on individual n-CdS NBs. The spatial distance between the ohmic electrodes on each NB was about 20  $\mu$ m. Third, a high- $\kappa$  dielectrics HfO<sub>2</sub> film (20 nm) was deposited to clad the NB by atomic layer deposition (ALD) method. Finally, an Au top-gate electrode ( $\sim$ 3  $\mu$ m wide, 100 nm thick) was made across the HfO<sub>2</sub>/NB in between the In/Au electrodes by a similar process as mentioned above. Here, two kinds of CdS NBs, labeled as NBs A and NBs B, were employed to fabricate the two types of MOSFETs used in the inverter. The electron concentrations of NBs A were around  $1 \times 10^{16}$  cm<sup>-3</sup>, while those of NBs B were around 5  $\times$  10<sup>16</sup> cm<sup>-3</sup>. The electron concentrations of the CdS NBs can be obtained by measuring CdS NB back-gate FETs before depositing the HfO<sub>2</sub> layer.<sup>18</sup> To construct highperformance inverters, the MOSFETs based on CdS NBs A were used as the loads, while those based on CdS NBs B were used as the drivers.

VOL. 3 • NO. 10 • 3138-3142 • 2009

Acknowledgment. The authors would like to thank Dr. W. L. Chen for improving the English writing of this paper. This work was supported by the National Natural Science Foundation of China (Nos. 60576037, 10774007, 10574008, 50732001), and National Basic Research Program of China (Nos. 2006CB921607, 2007CB613402).

## **REFERENCES AND NOTES**

- Bachtold, A.; Hadley, P.; Nakanishi, T.; Dekker, C. Logic Circuits with Carbon Nanotube Transistors. *Science* 2001, 294, 1317–1320.

- Sordan, R.; Traversi, F.; Russo, V. Logic Gates with a Single Graphene Transistor. Appl. Phys. Lett. 2009, 073305, 94.

- Ou, C. W.; Dhananjay; Ho, Z. Y.; Chuang, Y. C.; Cheng, S. S.; Wu, M. C.; Ho, K. C.; Chu, C. W. Anomalous *p*-Channel Amorphous Oxide Transistors Based on Tin Oxide and Their Complementary Circuits. *Appl. Phys. Lett.* **2008**, *122113*, 92.

- Mcalpine, M. C.; Friedman, R. S.; Lieber, C. M. High-Performance Nanowire Electronics and Photonics and Nanoscale Patterning on Flexible Plastic Substrates. *Proc. IEEE* 2005, 93, 1357–1363.

- Friedman, R. S.; McAlpine, M. C.; Ricketts, D. S.; Ham, D.; Lieber, C. M. High-Speed Integrated Nanowire Circuits. *Nature* 2005, 434, 1085.

- Javey, A.; Nam, S. W.; Friedman, R. S.; Yan, H.; Lieber, C. M. Layer-by-Layer Assembly of Nanowires for Three-Dimensional, Multifunctional Electronics. *Nano Lett.* 2007, 7, 773–777.

- Sun, Y.; Kim, H. S.; Menard, E.; Kim, S.; Adesida, I.; Rogers, J. A. Printed Arrays of Aligned GaAs Wires for Flexible Transistors, Diodes, and Circuits on Plastic Substrates. *Small* 2006, 2, 1330–1334.

- Wu, P. C.; Ye, Y.; Liu, C.; Ma, R. M.; Sun, T.; Dai, L. Logic Gates Constructed on CdS Nanobelt Field-Effect Transistors with High-κ HfO<sub>2</sub> Top-Gate Dielectrics. J. Mater. Chem. 2009, DOI: 10.1039/B909595K.

- Cui, Y.; Lieber, C. M. Functional Nanoscale Electronic Devices Assembled Using Silicon Nanowire Building Blocks. *Science* 2001, *291*, 851–853.

- Derycke, V.; Martel, R.; Appenzeller, J.; Avouris, P. Carbon Nanotube Inter- and Intramolecular Logic Gates. *Nano Lett.* 2001, 1, 453–456.

- Wang, D.; Sheriff, B. A.; Heath, J. R. Complementary Symmetry Silicon Nanowire Logic: Power-Efficient Inverters with Gain. Small 2006, 2, 1153–1158.

- Bachtold, A.; Hadley, P.; Nakanishi, T.; Dekker, C. Logic Circuits Based on Carbon Nanotubes. *Phys. E* 2003, *16*, 42–46.

- Chen, Z.; Appenzeller, J.; Lin, Y. M.; Sippel-Oakley, J.; Rinzler, A. G.; Tang, J.; Wind, S. J.; Solomon, P. M.; Avouris, P. An Integrated Logic Circuit Assembled on a Single Carbon Nanotube. *Science* **2006**, *311*, 1735.

- Ahn, J. H.; Kim, H. S.; Lee, K. J.; Jeon, S.; Kang, S. J.; Sun, Y.; Nuzzo, R. G.; Rogers, J. A. Heterogeneous Three-Dimensional Electronics by Use of Printed Semiconductor Nanomaterials. *Science* 2006, *314*, 1754–1757.

- Ryu, K.; Badmaev, A.; Wang, C.; Lin, A.; Patil, N.; Gomez, L.; Kumar, A.; Mitra, S.; Philip Wong, H. S.; Zhou, C. CMOS-Analogous Wafer-Scale Nanotube-on-Insulator Approach for Submicrometer Devices and Integrated Circuits Using Aligned Nanotubes. *Nano Lett* **2009**, *9*, 189–197.

- Ma, R. M.; Dai, L.; Huo, H. B.; Xu, W. J.; Qin, G. G. High-Performance Logic Circuits Constructed on Single CdS Nanowires. *Nano Lett.* **2007**, *7*, 3300–3304.

- Ma, R. M.; Dai, L.; Liu, C.; Xu, W. J.; Qin, G. G. Highperformance Nanowire Complementary Metal-Semiconductor Inverters. *Appl. Phys. Lett.* **2008**, *93*, 053105-1-3.

- Wu, P. C.; Ma, R. M.; Liu, C.; Sun, T.; Ye, Y.; Dai, L. Highperformance CdS nanobelt field-effect transistors with high-k HfO<sub>2</sub> top-gate dielectrics. *J. Mater. Chem.* **2009**, *19*, 2125–2130.

- 19. Shen, G. Z.; Chen, P. C.; Bando, Y.; Golberg, D.; Zhou, C.

Bicrystalline  $Zn_3P_2$  and  $Cd_3P_2$  Nanobelts and Their Electronic Transport Properties. *Chem. Mater.* **2008**, *20*, 7319–7323.

- Liu, C.; Wu, P. C.; Sun, T.; Dai, L.; Ye, Y.; Ma, R. M.; Qin, G. G. Synthesis of High Quality *n*-Type CdSe Nanobelts and Their Applications in Nanodevices. *J. Phys. Chem. C* 2009, *113*, 14478–14481.

- Keem, K.; Jeong, D. Y.; Kim, S. Fabrication and Device Characterization of Omega-Shaped-Gate ZnO Nanowire Field-Effect Transistors. *Nano Lett.* 2006, *6*, 1454–1458.

- Wang, D.; Wang, Q.; Javey, A.; Tu, R.; Dai, H. Germanium Nanowire Field-Effect Transistors with SiO<sub>2</sub> and High-k HfO<sub>2</sub> Gate Dielectrics. *Appl. Phys. Lett.* **2003**, *83*, 2432–2434.

- Lee, K. H.; Choi, J. M.; Lee, B. H.; Im, K. K.; Sung, M. M.; Lee, S.; Im, S. Low-Voltage-Driven Pentacene Thin-Film Transistor with an Organic – Inorganic Nanohybrid Dielectric. *Appl. Phys. Lett.* **2007**, *91*, 123502-1–3.

- Oh, M. S.; Hwang, D. K.; Lee, K.; Choi, W. J.; Kim, J. H.; Lee, S.; Im, S. Pentacene and ZnO Hybrid Channels for Complementary Thin-Film Transistor Inverters Operating at 2 V. J. Appl. Phys. 2007, 102, 076104-1–3.

- Cha, S. H.; Oh, M. S.; Lee, K. H.; Choi, J. M.; Lee, B. H.; Sung, M. M.; Im, S. ZnO-Based Low-Voltage Inverter With Quantum-Well-Structured Nanohybrid Dielectric. *IEEE Electron Device. Lett.* **2008**, *29*, 1145–1147.

- Fadlallah, M.; Benzarti, W.; Eccleston, W.; Barclay, D.; Billiot, G. Modeling and Characterization of Organic Thin Film Transistors for Circuit Design. J. Appl. Phys. 2006, 99, 104504-1-7.